通过瞬态电压抑制(TVS)二极管对敏感电子设备的静电放电ESD保护正成为各行业的常见电路技术,电路中可通过触摸(例如USB,HDMI等)访问的信号线需要对输入到某些IC的所有敏感信号线进行ESD保护。相对于它们所保护的IC,ESD保护二极管在电路板上的放置起着重要作用,重要的是要理解在诸如ESD的瞬态条件下PCB迹线信号的行为。

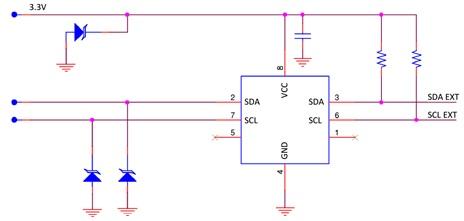

作为示例,图1中示出了具有TVS二极管的I2C总线扩展器的简单示意图。

图1 - TVS保护设备的通用原理图。

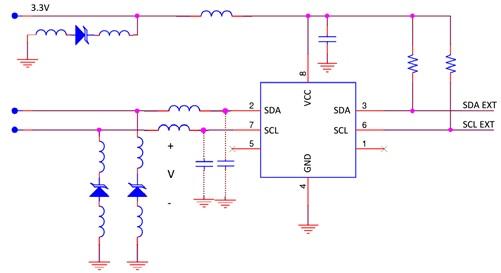

图2 - 显示走线电感和寄生电容的通用示意图的实际模型。

PCB走线将根据其长度具有与之相关的电感。考虑SDA信号跟踪。连接以下几点的迹线长度非常重要:

1.从节点A到二极管阴极的走线长度。

2.从二极管的阳极到接地连接的走线长度。

3.从节点A到IC输入引脚的走线长度。

换句话说,静电放电ESD保护二极管必须尽可能靠近它所保护的引脚放置,并且它与参考平面的连接必须尽可能靠近阳极引脚。否则,任何这些点之间的走线电感可能足够大,以至于由于IC的输入电容和走线的杂散电容,可能形成槽路。储能电路可能以超过IC输入电压能力的电压振荡,并可能对IC造成实质性损坏。

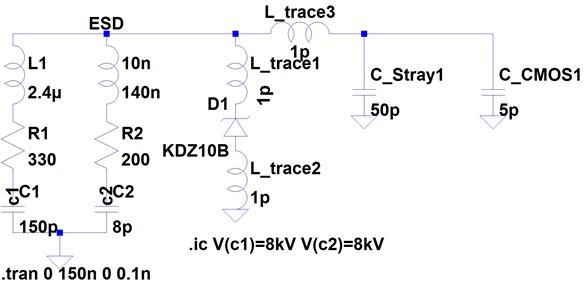

此方案在LTSpice中建模,图3显示了在LTSpice中创建的原理图,它由两部分组成,一部分是基于IEC 61000-4-2测试方法的ESD人体模型。第二部分是图2中跟踪SDA的表示,图3表示适用于二极管(10Vcmp),它在上面列出的所有点都适当放置,具有非常短的走线,因此产生非常小的走线电感。

图3 - 正确放置二极管的静电放电ESD电路模型。

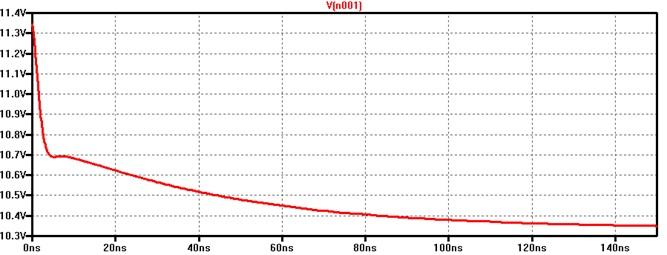

图4 - 正确放置二极管的CMOS输入电压。

当ESD保护二极管通过尽可能短的走线正确放置时,ESD脉冲被二极管钳位到安全水平。该二极管及其布局非常有效,可保护IC免受ESD影响。

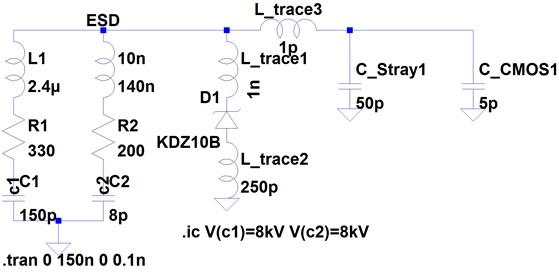

另一方面,图5显示了未正确放置的二极管(10Vclamp)的示意图,图2中从节点A到二极管阴极的迹线长约1英寸,估计约为1nH。从阳极到地面的痕迹约为0.03英寸,估计约为250 pH。图6显示了基于CMOS的输入电压(由电容表示)。

图5 - 不正确放置二极管的静电放电ESD电路模型

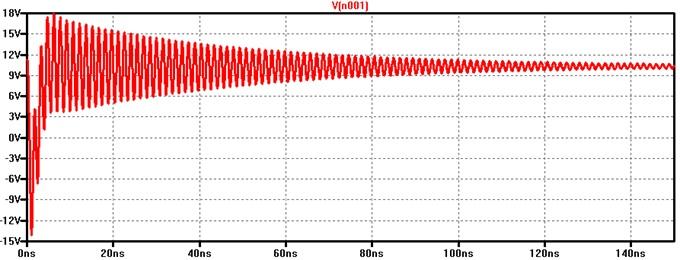

图6 - 未正确放置二极管的CMOS输入电压。

图6清楚地显示了将二极管阴极连接到信号线节点和二极管阳极连接到地的长迹线的影响。观察到的振荡峰值为21V,振铃频率由走线电感,线路的杂散电容和IC的输入电容决定。

结论

为了大限度地减少由于ESD引起的I / O线路振荡并避免IC损坏,必须确保以下内容:

1.钳位(TVS)二极管必须尽可能靠近IC引脚放置。

2.通向二极管阴极的走线必须尽可能短。

3.从二极管的阳极返回接地的走线必须尽可能短。

贝斯通检测科技是一家专业解决电磁兼容EMC测试的第三方检测公司,检测项目有静电放电测试、射频辐射测试(RS),干扰功率测试等,相关产品测试可在线咨询工程师!

认证电话:我们

阅读本文的人还阅读了:

1、电磁兼容emc测试项目:静电放电(ESD)测试

2、电磁兼容EMC设计技巧2: 连接器接地ESD