随着信息技术的不断发展,电子产品在功能,类别和结构方面变得越来越复杂,朝着多层方向和高密度方向推动PCB设计,因此,必须对PCB设计的EMC(电磁兼容性)给予很多关注,因为PCB的EMC设计不仅可以确保板上所有电路的正常和稳定工作,因此它们不会相互干扰,而是相互干扰。

还有效地减少了辐射传输和PCB的传导发射,以阻止电路受到外部辐射和传导的干扰,干扰是EMC重要的敌人,这篇文章会帮你解决电磁兼容问题。

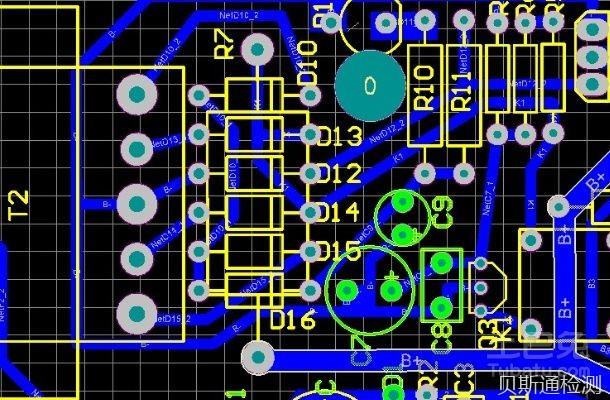

PCB电磁干扰可分为三类:

1)布局干扰是指由于PCB上不适当的元件放置而引起的干扰。

2)堆叠干扰是指由不科学的设置引起的噪声干扰。

3)路由干扰是指PCB信号线,电源线和接地线之间距离设置不当,线宽或不科学的PCB布线方法造成的干扰。

在PCB干扰分类方面,可以从布局规则,堆叠策略和布线规则的角度分别采取一些抑制措施,减少甚至消除PCB干扰的影响,以确保与EMC设计标准的兼容性。

基于分类的PCB干扰相应抑制措施:

1、布局干扰的抑制措施

停止布局干扰的特权在于合理的PCB布局,应符合以下六条规则:

a、每个功能模块的电路位置应根据信号电流位置合理设定,其流向应保持尽可能相同。

b、模块电路中的核心部件应设置在中心位置,并且应尽可能缩短元件之间的引线,特别是高频元件。

c、热敏元件和芯片之间的集成应远离加热元件。

d、连接器位置应根据板上的元件位置确定。连接器应放置在PCB的一侧,以阻止电缆从两侧引出,并减少共模(CM)电流辐射。

e、I / O驱动器应紧密靠近连接器,以阻止板上I / O信号的长距离路由。

f、热敏元件不能彼此靠得太近,输入和输出元件也应远离它们。

2、抑制堆叠干扰的措施

首先,PCB设计信息应该通过考虑的综合元素来控制,包括信号线密度,功率和接地分类,以确定功率和确保实现电路功能的层数,堆叠策略的质量基本上与地平面或电源平面的瞬态电压以及电源和信号的电磁屏蔽相关。

根据实际的堆叠设计经验,堆叠设计应符合以下规则:

1)地平面和电源平面应相互邻近,它们之间的距离应尽可能小。

2)信号平面应紧密靠近地平面或电源平面。单层或多层都可以。

在单层或双层PCB设计过程中,应仔细设计电源线和信号线,为了减小电流的回路面积,接地线和电源线应紧密相互靠近,并保持相互平行。对于单层PCB,应在重要信号线的两侧设置保护接地线。一方面,它旨在缩小信号的环路面积。另一方面,可以避免信号线之间的串扰。

对于双层PCB,也可以设置保护接地线,或者在重要信号的图像平面上实现大面积接地。尽管PCB制造和装配调试简单方便,但直接模拟复杂的PCB(如数字电路和数字模拟电路)是不可接受的,因为辐射会随着没有参考平面的环路面积的增加而增加。

如果成本足够,建议使用多层PCB,在多层PCB设计过程中必须遵循三条规则:

1)对于重要的信号线,例如具有强辐射的总线或时钟线以及具有高灵敏度的线路,应在两个接地平面之间或紧靠接地平面的信号平面上实现布线,这有利于信号环路区域收缩,辐射强度降低和抗干扰强化。

2)应确保边缘辐射得到有效控制。与相邻的接地层相比,电源面应在内部减小5至20H(H表示电介质厚度)。

3)如果底层和顶层之间存在高频信号线,则应将它们布置在顶层和地平面之间,以防止高频信号线辐射到空间。

3、路由干扰的抑制措施为了禁止干扰,在路由方面必须遵守以下规则:

1)输出端子和输入端子的引线应避免长距离并联。通过增加接地线或增加线之间的距离可以减少并联串扰。

2)路由宽度永远不会突然改变。角应为弧形或天使度为135°。

3)随着环路面积,电流和信号频率的增加(减小),载流环路的外部辐射增加(减少),因此当电流流过时必须减小引线环路面积。

4)应增加引线长度,同时增加宽度,以降低引线的阻抗。

5)为了大限度地降低相邻线路之间的噪声耦合和串扰,请在线路之间进行隔离处理,以确保布线隔离。

6)应设置分流隔离键信号,并通过保护电路保护键信号。

此外,当路由信号线,电源线和接地线时,请遵循路由规则,根据自身的特点和功能:

a、公共接地线应布置在PCB边缘,网状或环形; 接地线应尽可能厚,并应涂上更多的铜箔,以加强屏蔽效果; 模拟接地应采用数字接地隔离,单点并联应应用于模拟地的低频接地。多点串联应适用于高频地。在实际路由中,串联连接可以与并联连接组合。

b、应尽可能增加电源线的宽度,并应减小回路电阻,以确保接地线和电源线的方向与数据传输方向之间的同步。对于多层PCB,应减少电源线与地平面或电源平面之间的距离。应该独立地为每个功能单元供电,并且由公共电源供电的电路应该彼此接近并且相互兼容。

C、信号线应尽可能短,以确保减少干扰信号耦合路径,时钟信号线和敏感信号线应首先布线,然后是高速信号线,后是无关紧要的信号线。如果信号线彼此不兼容,则应实施隔离处理以停止产生耦合干扰,关键信号路由不能超过由焊盘和通孔过孔引起的分离区域或甚至参考平面空间。否则,信号回路区域将增加,同时,为了禁止边缘辐射,键信号线和参考平面之间的距离不能小于3H(H指的是键信号线和参考平面之间的高度)。

我们唯一要担心的是害怕不成功,对于电子工程师来说,在PCB设计过程中,干扰总是让你烦恼。但是,只要我们知道干扰源自何处并采取有效措施,绝对会在完全实现PCB性能的情况下降低干扰。

贝斯通检测科技是一家专业解决电磁兼容EMC认证问题的第三方检测机构,总部位于沙井新桥,有相关产品EMC测试可咨询工程师!

认证电话:我们

阅读本文的人还阅读了:

1、高速PCB布线技术,以减少电磁干扰EMI的影响

2、单层PCB,双层PCB和多层PCB方面的电磁兼容性EMC设计