新一代电子技术可以提高组件的高边缘速度,电路工作速度的提高对PCB设计提出了越来越高的要求,PCB设计的质量甚至决定了元件和整个电路的工作性能,特别是考虑到成本和PCB面积以及综合电路的功能,电磁干扰EMI(电磁接口)产生的来源越来越广泛,机制复杂。

电磁干扰EMI机制和解决方案

EMI的主要元素包括电磁干扰源,传输路径和干扰对象,由于元件导致EMI的出现,有必要确定易于分辨的元件和那些只能在PCB设计过程中部分解决的元件,以便在布局,布线过程中考虑它们和接地。

1、布局

在PCB布局方面,应根据不同的功能划分区域。不同的功能分布在不同的区域,同时必须特别注意功能区域的敏感单元。

通常PCB布局必须遵循以下原则:

a、在高速电路中,必须考虑元件引脚分布的参数,并且元件引脚的分布容量对于高速时钟信号尤为重要。同时,必须考虑分布电感,因为它可能导致信号振荡,从而导致电路功能失效。因此,在布局过程中,必须以高密度布置分布,降低引线长度以便将来布线,并且EMI的影响降低。

b、如果模拟组件和电子组件都保留在电路中,则它们必须在布局过程中独立分配。由于数字元件的信号具有复杂的复合材料,存在多个谐波,因此对模拟信号产生很大的影响。因此必须非常谨慎地考虑它们。

C、时钟单元在高速电路中至关重要。时钟单元的工作机制实际上相当于噪声源,这意味着当满足某些条件时,该单元将振荡。作为导电干扰和辐射干扰的重要来源,时钟单元不得放置在PCB的边缘。否则,EMI会变得如此严重。有必要将时钟单元放置在PCB的中心,这可以大大降低电路中的EMI。

2、路由

在PCB布线过程中,在低成本的情况下,可以尽可能地扩大接地面,以减少EMI的影响,但是,在严格控制成本的情况下,必须仔细考虑PCB层数和堆叠顺序。此外,必须考虑信号类型,并且必须独立地对高速信号和低速信号执行路由。此外,还必须考虑其他因素,包括噪声源和如何加强噪声抑制,阻抗匹配问题(没有合适匹配的高速信号肯定会导致信号反射并降低电路的可靠性),以及网表。

a、路由的基本原则路由遵循的一般原则包括:

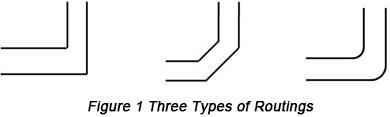

1)布线时应避免使用断点,这意味着应避免使用直角,如下图1所示。

PCB布线类型

由于直角可能会导致反射,因此应设计平滑的拐点以避免这种现象。同时,关键信号不得超出分割区域,否则EMI将立即增强。常见的信号旁路是跨越不同的功率划分区域。

2)在布局过程中,模拟元件和数字元件需要相互分开,这意味着应该划分它们的布线。同时,地线和电源线的宽度应扩大,一般规则是地线的宽度大于电线的宽度大于信号线的宽度。此外,3W原理应充分考虑信号线的布线,而对于多层板,在内层应考虑20H原则,完成上述工作可以避免70%的EMI。就模拟敏感线而言,可以采取措施,例如接地。

3)对于USB2.0或其他高速差分线路的布线,应采用耦合布线,保证差分对之间参考面的完整性。由于差分对通常是高速信号,因此不应将布线布置在PCB的边缘。

b、循环

在PCB设计中永远无法避免循环。循环由流出的信号形成,并且每个环在功能中起到天线的作用。为了降低PCB中的EMI,应该减少环路的数量和环路的天线能力。这意味着在PCB设计中应了解每个信号的流向,并且必须降低高速信号的环路面积。

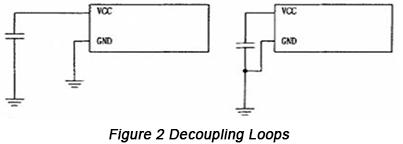

在电路中,常用的环路位于去耦电容所包含的功率环路中,如图2所示。

解耦循环

如果将去耦电容放置在图2中的左图中,则会产生相对较大的电流环,并出现明显的EMI现象。相反,在图2的右图中,去耦电容紧邻芯片放置,产生极小的去耦回路,其主要功能是降低电磁干扰EMI。显示应遵循的原则以减少循环:

1)每条信号线上的两点之间只保证一条路径。

2)在确保信号回路的情况下,应该使用地平面,没有阻塞。

C、PCB的地线

1)在PCB接地系统中,数字接地,模拟接地和系统屏蔽接地之间应区分不同。磁珠和电容器用于分离数字地和模拟地,数字地和场地应直接连接。

2)如果允许,接地线应在PCB上加宽。

3)通过地线进行闭合电路,以增强抗干扰能力,降低系统间的电平差。

3、过滤器设计

在高速PCB中,可以在电源线和信号线上实现滤波处理。常见的措施包括增加磁性过滤器组件,EMI滤波器和去耦电容器。

普通滤波电路

a、选择去耦电容

1)在电路中,去耦电容有助于使功率平稳,增强抗干扰能力。通常,陶瓷电容器由于其高稳定性,高精度,小体积和低ESR(等效串联电阻)而被选为去耦电容器。在电路设计中,电阻值选择在1μF至100μF的范围内,同时必须根据电路考虑耐压能力。

2)去耦电容必须紧密放在元件旁边。

b、选择磁性元件

磁性元件可分为电感器和磁珠,通常,电感器在电源端子的末端被拾取,而信号线之间的磁珠被拾取。在元件选择过程中,必须考虑饱和参数。一旦磁性元件达到饱和状态,它们就会被烧毁。此外,必须考虑磁性部件的质量和DCR参数。

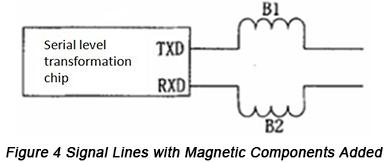

信号线中常用的措施在于在串行线上应用磁珠以增强EMI容量。

添加了带磁性元件的信号线

C、选择EMI滤波器

具有严重共模干扰的区域在于有电源输入和信号线输出的地方。避免共模干扰的一般措施包括增加共模电感,压敏电阻,LC电路和特定的EMI滤波器。在高速电路中,必须考虑在USB和HDMI等数字接口上进行高速传输时的EMI问题。

4、信号反射

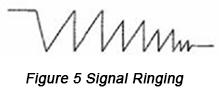

在信号传输中,总是期望源端子处的能量被传输到装载端子,这意味着ZL应该等于ZO。如果它们彼此不相等,则会反映部分能量。如果线路的传输延迟相对较长,则较强的信号将被反射回源终端。然后,当产生振铃时,必须改变相对大的量以进行补偿,如下面的图5所示。

信号振铃

当信号振铃时,电磁干扰EMI达到严重程度的峰值,为避免PCB设计中出现此类现象,请遵循表下面的原则。

信号边沿时间(ns) 信号线长度(英寸)

5 8.6

4 6.9

3 5.1

2 3.4

1 1.7

电磁干扰EMI测试

产品设计完成后,尽管有很多措施可以避免电磁干扰EMI,但在实施测试之前不会发现问题,然后可以进行一些修改来解决问题。

EMI测试包括测试方法,设备和测试位置,测试方法应参考所有项目。如果设备无法达到标准,可以使用光谱仪进行定性测试,如果需要特定的设备电磁干扰EMI值,则必须使用专业设备。至于测试位置,好在暗室进行测试。

贝斯通检测科技总部位于深圳,有大型的电磁兼容EMC实验室,认监委授权CNAS机构,上千种产品EMC认证整改经验,提供设计指导,详情咨询工程师!

认证电话:我们

阅读本文的人还阅读了:

1、电磁兼容EMC的基础知识:什么是串扰?

2、电磁兼容知识:EMC标准和法规的演变