电磁兼容EMC基础知识和实用的PCB设计技巧

虽然经常用作同义词,但电磁兼容性(EMC)实际上是辐射和传导电磁干扰(EMI)的控制; 而糟糕的EMC是PCB重新设计的主要原因之一。实际上,估计有50%的首次运行的电路板发生故障,因为它们要么发出不需要的EM和/或对它敏感。这很可能是因为某些行业(例如医疗和航空航天)的严格法规,或者因为正在开发的产品要加入历史上一直考虑EMC设计的产品线。例如,移动电话开发人员生活和呼吸无线连接,并且精通小化不必要辐射的风险。

EMC问题严重的是那些用于白色家电的PCB的设计者 - 例如烤面包机,冰箱和洗衣机 - 它们加入了与物联网无线连接的众多互联网设备,由于涉及的产品产量大,重新设计PCB可能会导致产品发布延迟。更糟糕的是,产品召回可能会对公司的声誉和财务造成严重损害。

所以产品设计之初就综合考虑周全EMC问题,会给您的产品设计节省很多费用!

噪音来自哪里?

考虑到EMC的设计并不缺乏指导,许多公司都有自己的内部PCB设计和EMC规则,指导也可以来自外部来源,例如立法机构,IC供应商和客户。但是,以面值接受所有指南可能会导致过度防御的EMC策略,并导致项目延迟。应单独评估规则以确定它们是否适用于当前设计。

也就是说,自己具备一点EMC设计基本常识对设计会有很大班助,例如,为了抑制PCB上的噪声源,您应该:

1.保持时钟频率尽可能低,上升边缘尽可能慢(在需求规格范围内);

2.将时钟电路放置在电路板中央,除非时钟必须离开电路板(在这种情况下,时钟必须靠近相关连接器);

3.安装时钟晶体与面板齐平并研磨;

4.保持时钟循环区域尽可能小;

5.将I/O驱动器定位在信号进入/离开板的点附近;和

6.过滤所有进入板的信号。

虽然上述措施将有助于缓解一些常见的EMI问题,但每个有源PCB仍将辐射EM能量。这是因为每个电流都产生磁场,每次充电都会产生电场。总辐射将是信号环路差模辐射,共模辐射(电压和电流驱动)和配电系统(PDS)产生的辐射之和。

你应该更详细地研究这些:

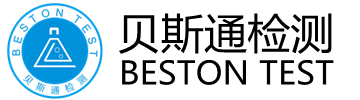

1、差模辐射是由传输线环路引起的,信号产生的是差分电流(见图1)。对策包括使用屏蔽层(Vcc或接地),在内层放置关键信号(也称为条带线),避免信号的长并行运行,如上所述,小化环路面积并保持信号上升和下降时间与可能。

图1:差模辐射

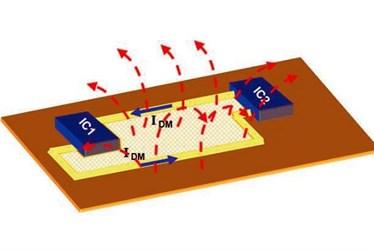

2、共模辐射通常是更为关键的EMC设计方面,因为EMI在远场中更“可见”。它由寄生电流(例如,通过磁通耦合的开关电流或感应电流)或寄生电压(例如到有源IO信号的串扰电压)产生。对策包括去除那些寄生电流和电压的来源 - 从而避免快速切换信号之间的串扰 - 以及更智能的元件布局和布线,以避免磁通耦合和包裹效应。

图2:共模辐射

3、对于PDS,它可以辐射,因为PCB本质上是一个LCR谐振器,包括电感元件(轨道),电容(接地和电压平面就像电容器的极板)和电阻。PDS EMI的对策包括降低电路板阻抗,避免电感并确保足够的去耦。

此外,IC也是EMI的来源,并将有助于PCB的EM配置文件。在IC选择期间必须考虑到这一点,芯片供应商应该能够为您提供有关电路EMI行为的信息。

规则检查器和模拟

许多PCB设计工具包括EMC规则检查器,检查包括查看可能发生信号串扰的实例的设计数据几何(由于并行路由的迹线),很少或没有屏蔽的情况,以及可能需要去耦的情况。

这些规则将包含许多EMC工程师的“技术诀窍”。但是,了解它们的起源以及CAD工具供应商如何实现它们非常重要; 并且您有权要求查看供应商的规则书。这些工具还应该可以突出显示EMI抑制和EMC完整性至关重要的PCB区域 - 您可以告诉工具您的优先级。

但是,我们不要忘记,这些都是布局后检查。好以EMI和EMC为设计理念,而不是进行试错练习。此外,如果有任何可能的EM辐射水平,您将收到很少的指导。

要进行更高级的分析,需要进行模拟,与EMC设计规则检查器一样,结果的意义和价值将取决于电路板的数字表示及其行为的呈现程度,当然还有各种EM方程作为软件算法实现的程度。同样,工具供应商应该能够提供信息。您还应该采取一些有代表性的测量来验证模拟方法,并编制指标作为解释未来结果的基础。

市场上有许多数字3D EM仿真工具,其中一些专用于天线设计等特定活动,它们非常适合假设研究和结构优化。他们可以为给定结构建模所有EMI效应,但它们确实需要相当大的计算能力(内存和CPU时间),并且往往会花费很多。此外,需要深入了解EMI以理解结果,因为有时难以单独使用3D EM结果来解释特定辐射峰值的原因。

但是,对于白色家电中使用的PCB类型,我们并不寻求优化天线结构或产生特定的射频曲线; 我们只是希望验证电路板设计是否具有良好的EMC - 并且具有良好EMC规则检查器的PCB设计CAD工具就足够了。

如何设计电磁干扰EMI?

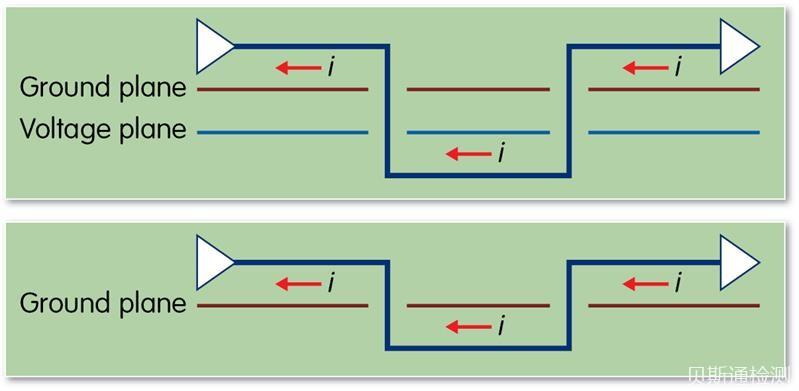

尽管EMC没有灵丹妙药,但良好的设计工作应包括识别寄生EMI天线,如电偶极子。此外,识别当前路径,因为电流在循环中流动并始终寻找阻力小的路径。因此,计划适当的返回路径(注意'地面'不是EMC工程中可接受的技术术语)并避免交叉分裂/间隙(即使是差分对)和返回路径不连续(见图3)。

图3:在顶部图中,参考层从地平面变为电压平面,用于部分迹线。这产生了EMI天线。保持相同的参考平面,如下图所示,避免/减少返回路径的不连续性。

总而言之,好以EMC为设计目标,而不是冒险重新设计电路板,但您必须清楚地了解哪些EMC规则适用于您的项目。此外,在PCB设计CAD工具中嵌入EMC分析功能可以在制造电路板后大大降低EMC合规性失败的风险; 但请确保该工具的规则检查程序基于经过充分记录和验证的EMC原则和解释。除非a)您信任模拟器并且b)您对结果的感受有所了解,否则永远不要模拟。

贝斯通主要帮客户解决电磁兼容性测试问题,涉及到电磁兼容emc的整改,FCC无线认证等!

详情咨询工程师:我们

阅读本文的人还阅读了:

1、EMC设计解决高速PCB中的偏移源问题

2、什么是谐波,谐波是怎么产生的?