ESD测试通常作为一般CE测试要求,也适用于其他产品特定的标准。特别是,应用于I/O连接器的底盘接地连接的静电放电显示不成比例的故障数量。这些故障通常以设备复位的形式出现,或者更糟——“性能的永久性下降”,也就是说,它烧毁了一些重要的东西。

根据相邻表,采用根ESD测试标准(61000-4-2),将ESD脉冲采用“接触放电”的方法应用于连接器的外露金属壳。这些通常通过连接器连接到PCB底盘接地。放电脉冲的振幅取决于你的产品标准,但通常是4kV或8kV的大多数应用。

以下是几个EMC设计规则的详细说明,以避免这个非常常见的问题:

1.确定ESD测试地点

为了在正确的地方对你的产品应用ESD保护,你应该知道测试实验室要在哪里“消灭”它。

除非在通用、产品相关或产品系列标准中另有规定

静电放电只适用于EUT的点和表面

在正常使用期间,可接近的人。

这就是说,如果你能用手指够到它,那么它就应该被测试。测试实验室会对你的产品外壳做一些探索性的测试,看看他们是否能找到任何易感位置。如果底盘是不导电的,那么通常不会有很多放电点。

即使在不导电的底盘,有一些常见的放电点:

1.连接器

2.螺杆头

3.按钮/键盘

4.底盘的两部分接合在一起

5.内部多氯联苯接近底盘的地方

6.led或图形显示器

在8kV或16kV时,电弧距离可能相当远,所以即使通过一个不导电的外壳,放电也有可能找到通往电路板的路。

确定“公共服务电子化”的水平

ESD测试级别通常由适用于您的产品的产品标准设置。例如,消费者音频EMC抗扰度标准为EN55103-2,其中ESD测试级别定义为几乎所有使用环境下的8kV空气放电和4kV接触放电。

选择正确的瞬态抑制器

一旦你知道放电测试的水平和放电的地方,你可以继续为你的电路板选择一些ESD保护。您可以参考我们EMC设计指南电子书的4.6.1部分,其中详细介绍了这些选择。有很多选择,包括火花间隙,电阻,电容,变阻器和电视二极管等。一个好的ESD抑制器会将设备上的大电压压到一个已知的水平,并将多余的能量转化为热量或噪音。

在正确的位置申请

ESD抑制-优秀的EMC设计技术的一个关键方面,有时被忽视的是ESD保护的位置。它必须在物理上尽可能靠近放电事件将要发生的区域。这将使放电位置和瞬态抑制器之间的任何路由的串联电感降至低。

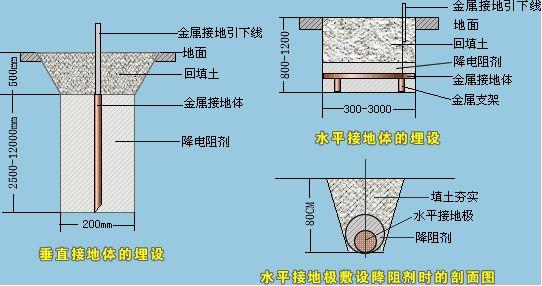

正确设计排放路径

底盘地面布置图:重要的是要使连接器上的底盘地面上的放电路径形象化。对于许多设计,底盘地面与主板地面是分开的,出于安全考虑,甚至是为了处理ESD。一个久经考验的方法是把你的电路板地面上的底盘接地带回主电源输入,这样任何放电都可以通过这一点消散,而不会影响你的电路的其余部分。

贝斯通是一家专业提供电磁兼容测试整改服务的第三方检测公司,认监委授权cnas资质,大型emc实验室满足各种测试需求,相关产品测试可在线咨询工程师:我们

阅读本文的人还阅读了: